PhySim Electronic Technology Co., Ltd.

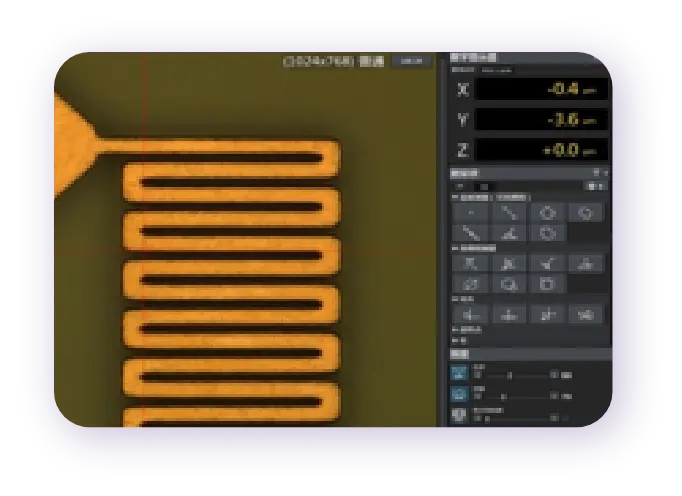

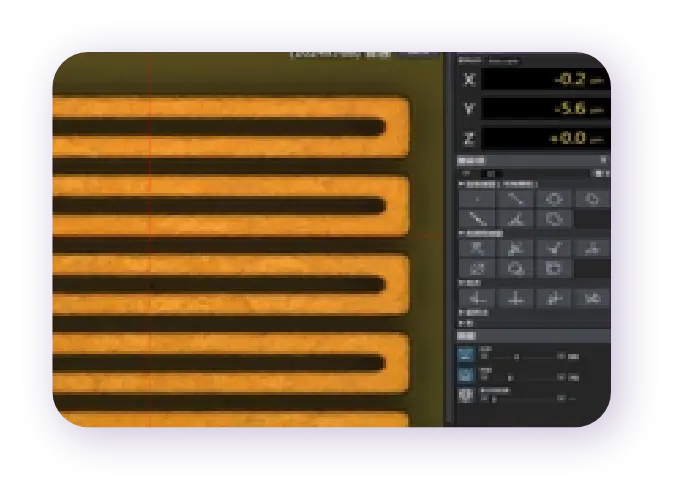

常规FC Bumping深圳中科实现最小间距80um量产;

Micro Bumping实现40um量产,开发完成25um间距。

|

晶圆级封装

Wafer Level Package

|

||||

|---|---|---|---|---|

|

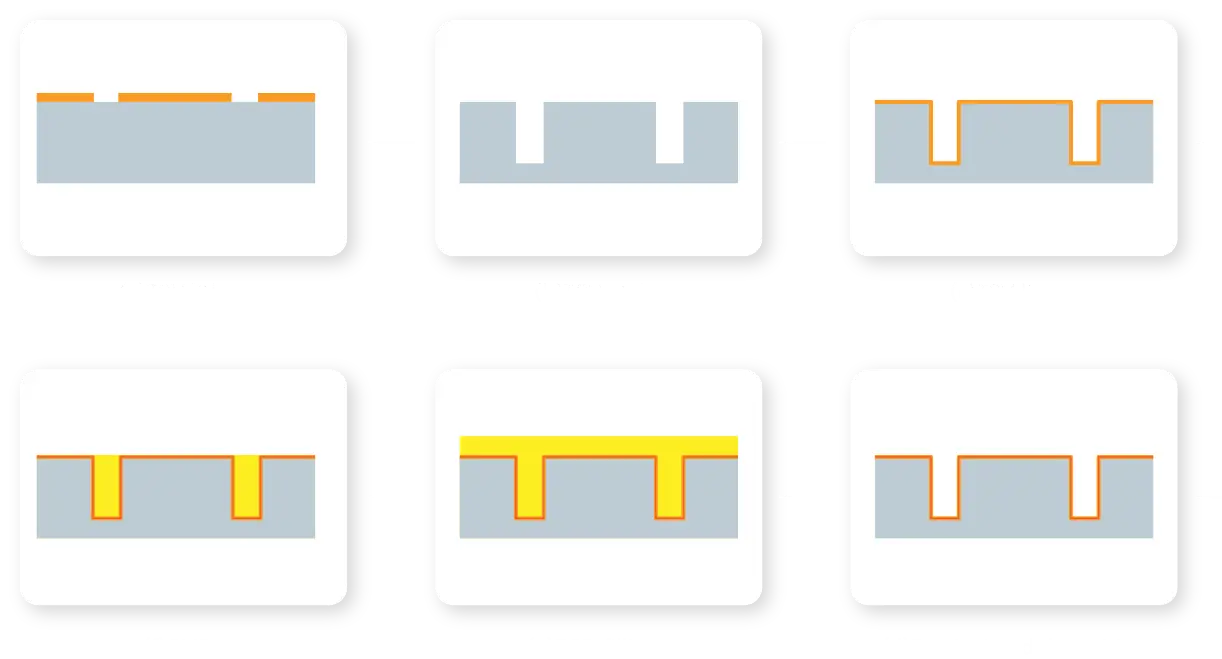

凸块

Bumping

|

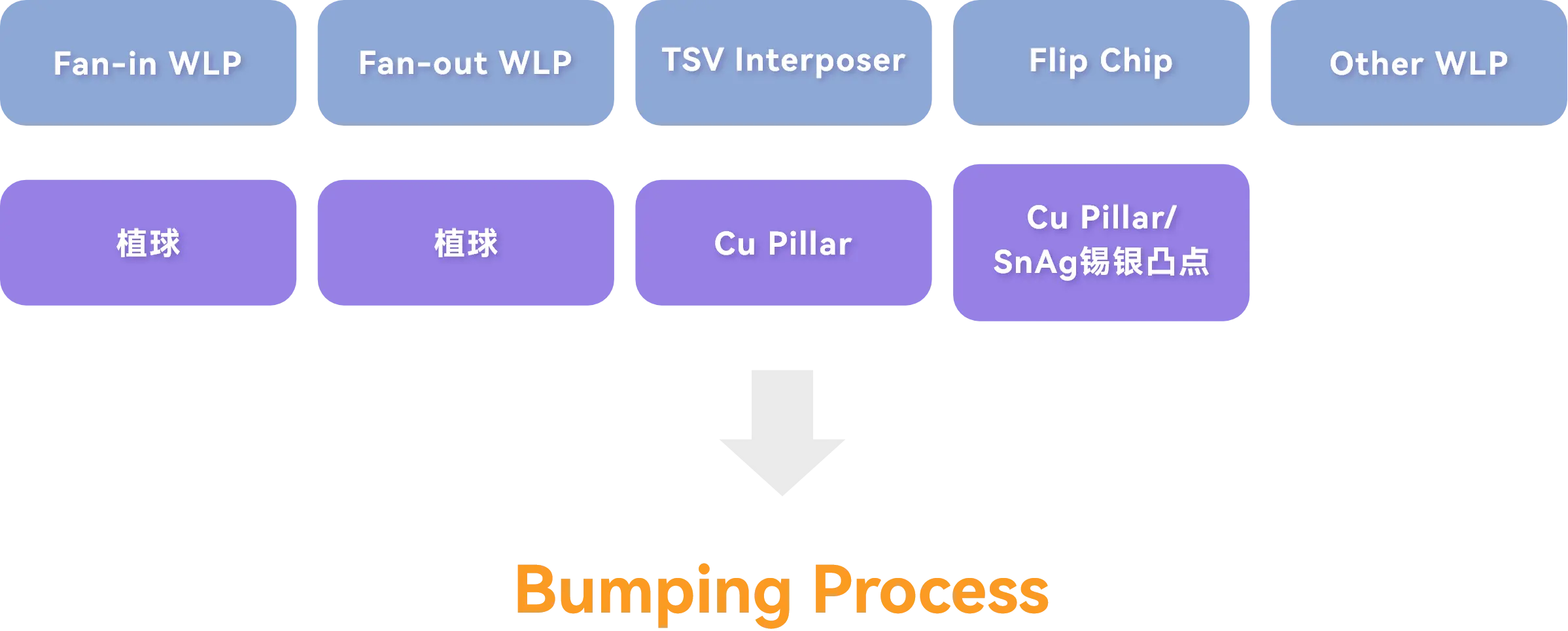

扇入型晶圆级封装

Fan-In WLP

|

扇出型晶圆级封装

Fan-Out WLP

|

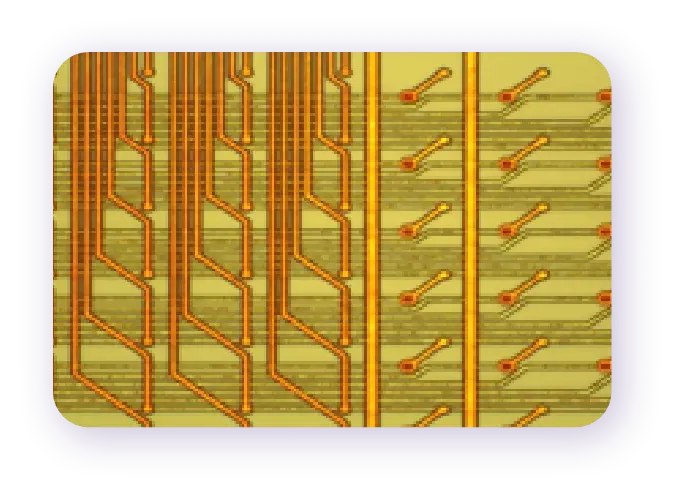

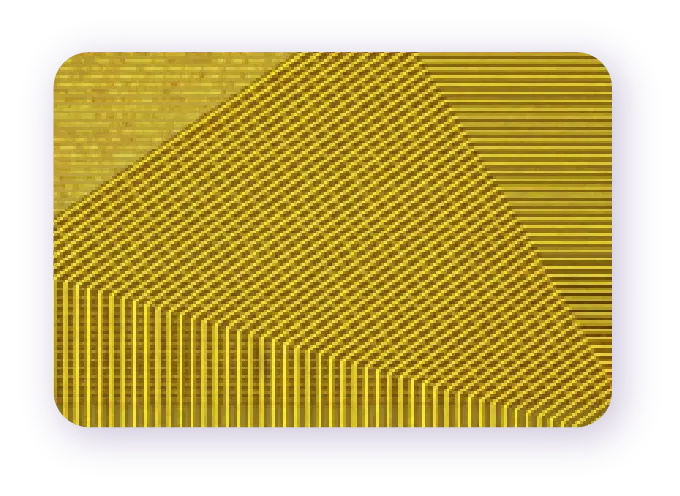

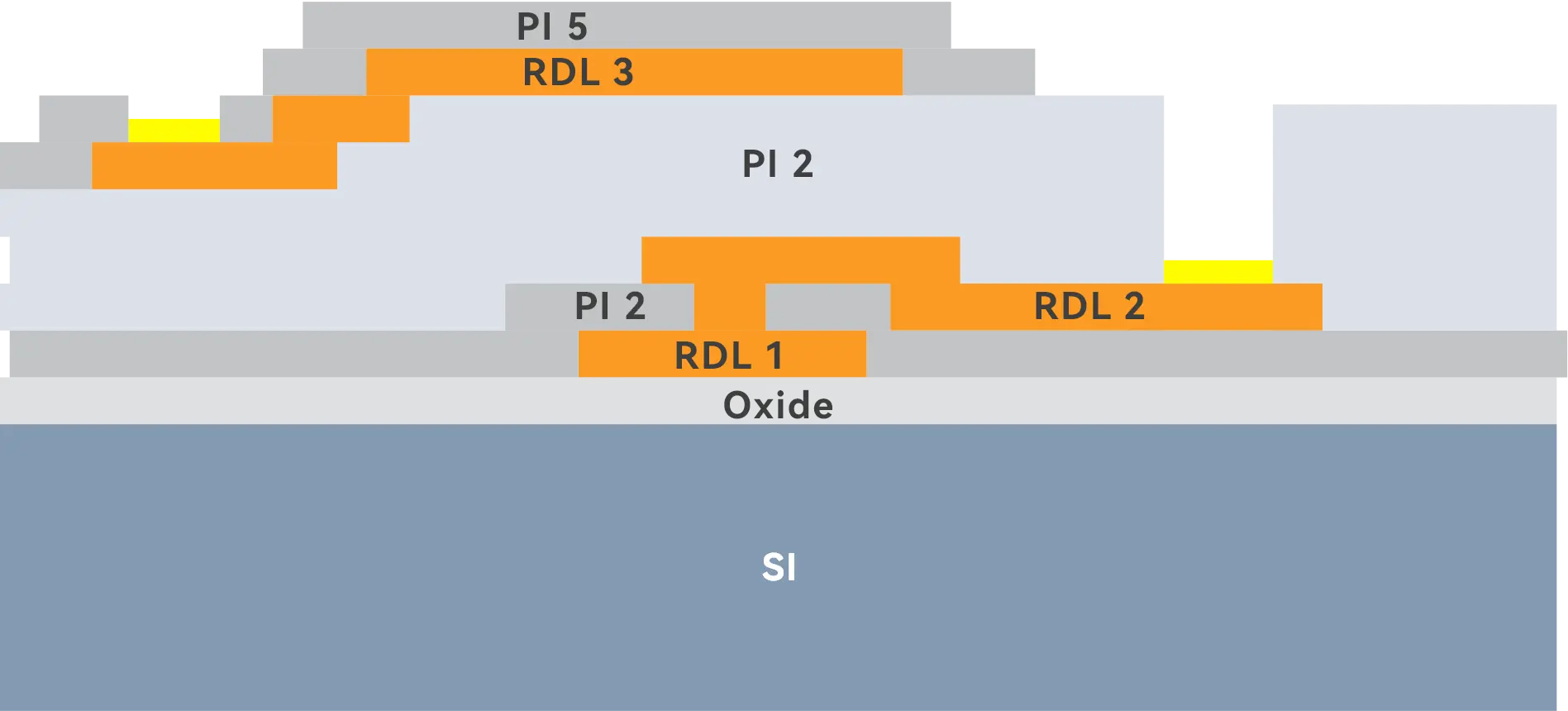

硅转接板

TSV Interposer

|

直孔晶圆级封装

Via Last TSV WLP

|

|

8”/12”

Cu Pillar

|

8”/12”

1P1M

|

12”

|

MAX

10:100 TSV

Interposer

|

12”

CIS TSV WLP

|

|

8”/12”

Sn-Ag

|

8”/12”

2P2M

|

8”

MEMS TSV WLP

|

||

|

12” Au

(Planning)

|

12”

FI TSV WLP

|

|||

|

12”

u-Bump

|

||||

| SiP封装设计/基板设计/电、热、应力仿真 | ||||

| 失效分析试验室 | ||||

| 可靠性分析实验室 | ||||